Volume-2 | Issue-6 | December: 2025

# Original Researcher Article

# **Towards Next-Generation Chiplet Systems: Advances in Heterogeneous Integration and Packaging Technologies**

# Pradeep Chhawcharia <sup>1</sup>, Mohammad Sabir <sup>2</sup>, Ishita Sharma <sup>3</sup>, Himani Katariya <sup>4</sup>, Sumedha Soni<sup>5</sup>, Divyansh Mehta<sup>6</sup>

<sup>1</sup>dept. of Electronics & Communication Geetanjali Inst. of Tech. Studies Udaipur, India

Email ID: <a href="mailto:hodece@gits.ac.in">hodece@gits.ac.in</a>.

<sup>2</sup>dept. of Electronics & Communication Geetanjali Inst. of Tech. Studies Udaipur, India

Email ID: sabii.sankhla@gmail.com.

<sup>3</sup>dept. of Electronics & Communication Geetanjali Inst. of Tech. Studies Udaipur, India.

<sup>4</sup>dept. of Electronics & Communication Geetanjali Inst. of Tech. Studies Udaipur, India

<sup>5</sup>dept. of Electronics & Communication Geetanjali Inst. of Tech. Studies Udaipur, India

<sup>6</sup>dept. of Electronics & Communication Geetanjali Inst. of Tech. Studies Udaipur, India

#### ABSTRACT

The slowdown of Moore's Law and the breakdown of Dennard scaling have compelled the semiconductor industry to seek new paradigms for building powerful and efficient computing systems. A leading solution is the chiplet-based architecture, which abandons the monolithic System-on-Chip (SoC) approach in favor f integrating smaller, specialized dies—known as chiplets—within a single package. This method, termed Heterogeneous Integration (HI), improves manufacturing yield, reduces cost, and allows for the "mix-and-match" of optimal process technologies for different functions. However, this shift introduces critical challenges in interconnect design, thermal management, and system security. This paper reviews the foundational technologies enabling modern chiplet systems, including 2.5D and 3D packaging, and analyzes emerging interconnect standards like Universal Chiplet Interconnect Express (UCIe). We also discuss the pivotal role of AI/ML in design automation and explore future directions such as co-packaged optics and sustainable design. Finally, we provide an outlook on the evolution towards an open, interoperable chiplet ecosystem.

**Keywords**: Chiplet, Heterogeneous Integration, Advanced Packaging, UCIe, 2.5D/3D Integration, Thermal Management, AI/ML Co-Design.,

# 1. INTRODUCTION:

For decades, the semiconductor industry thrived by scaling transistors onto ever-larger single dies, a trend famously described by Moore's Law. However, this monolithic approach is now hitting fundamental physical and economic walls. As transistor sizes shrink below 5 nanometers, manufacturing yields drop, and costs soar. Furthermore, the inability to power all transistors on a large chip simultaneously—a problem known as "dark silicon"—limits performance gains [1].

In response, the industry is undergoing a paradigm shift towards chiplet-based design and Heterogeneous Integration (HI) [2]. Instead of one large SoC, a system is partitioned into smaller, modular chiplets. Each chiplet is a pre-tested functional block (e.g., a CPU core, GPU, memory, or I/O controller) fabricated on the most suitable and cost-effective technology node. These chiplets are then integrated into a single package using advanced techniques, creating a system that can outperform a monolithic design. This approach, successfully demonstrated in commercial products like AMD's EPYC processors and Intel's Ponte Vecchio, offers superior yield, reduced cost, and the flexibility to combine specialized technologies [3, 4].

This paper provides a comprehensive overview of the technologies driving next-generation chiplet systems. We

explore core packaging methods, the critical role of interconnect standards, and the challenges of thermal management and security. We also highlight the growing use of AI/ML in design and discuss emerging trends, concluding with a perspective on the future of this dynamic field.

# **Chiplet-Based Architectures and Integration Technologies**

A chiplet is a small, functional die designed to operate collaboratively with other chiplets inside a single package. Heterogeneous Integration is the process of assembling these disparate chiplets into a cohesive system. The performance and efficiency of the final system are heavily dependent on the integration technology used. The primary methods are illustrated in Figure 1 and detailed below.

A. 2D Integration: Chiplets are placed side-by-side on a standard organic substrate. This is the simplest and most cost-effective method but offers limited connection density and bandwidth between chiplets. It is often used in Multi-Chip Modules (MCMs).

B. 2.5D Integration: Chiplets are placed side-byside on a passive silicon interposer. This interposer, which contains a dense network of microscopic wires and Through-Silicon Vias (TSVs), acts as a high-density communication bridge between the chiplets, enabling much higher bandwidth and lower latency than 2D. This

is the dominant method for high-performance computing [5].

C. 3D Integration: Chiplets are stacked directly on top of each other, connected by TSVs or advanced direct bonding techniques like hybrid bonding. This offers the highest connection density, shortest interconnect paths, and best performance-per-watt, but introduces significant thermal challenges [6].

Fig. 1 : Conceptual diagrams of (a) 2D, (b) 2.5D, and (c) 3D chiplet integration schemes (adapted from Shim & Oh, 2022) [26].

**Industry Examples:**

- AMD EPYC CPUs: Utilize a central I/O chiplet on a mature node surrounded by multiple CPU core chiplets on an advanced node, interconnected via a 2.5D architecture and the Infinity Fabric protocol [3].

- Intel Foveros: An active 3D stacking technology that allows logic chiplets to be stacked on top of a base die, enabling new form factors and performance tiers [4].

- TSMC CoWoS: A leading 2.5D packaging technology that places chiplets on a silicon interposer, widely used by companies like AMD and NVIDIA [5].

#### **Advanced Packaging and Interconnect Standards**

Advanced packaging is now a primary enabler of system performance, moving beyond its traditional role of mere protection.

3.1. Key Packaging Technologies

TABLE I. COMPARISON OF ADVANCED PACKAGING TECHNOLOGIES.

| Technol ogy                                   | <b>Descr</b> iption                                                | Key<br>Feature                         | Ad<br>van<br>tag<br>e                                                | Challanga                      |                                |

|-----------------------------------------------|--------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------|--------------------------------|--------------------------------|

| 2.5D w/ Silico n Interp oser                  | Chiple ts on a passiv e silicon bridge with TSVs.                  | High-den:<br>wiring lay                |                                                                      | High bandwidth, proven in HPC. | Cost, limited interposer size. |

| Silico<br>n<br>Bridg<br>e (e.g.,<br>EMIB<br>) | Small silicon pieces embed ded in substr ate under chiple t edges. | Localiz ed high-density intercon nect. | Cos<br>t-<br>effe<br>ctiv<br>e<br>vs.<br>full<br>inte<br>rpo<br>ser. |                                | gn.                            |

| 3D w/<br>Micro<br>bumps         | Dies<br>stacke<br>d and<br>conne<br>cted<br>with<br>small<br>solder<br>bumps | Vertical die stacking .        | Hig<br>her<br>den<br>sity<br>tha<br>n<br>2.5<br>D.                                | Thermal resistance, bump pitch limits. |

|---------------------------------|------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------|----------------------------------------|

| 3D<br>Hybri<br>d<br>Bondi<br>ng | Dies<br>fused<br>directl<br>y with<br>Cu-to-<br>Cu<br>bonds.                 | Sub-<br>10µm<br>bond<br>pitch. | Hig<br>hest<br>den<br>sity<br>,<br>best<br>perf<br>orm<br>anc<br>e/p<br>owe<br>r. | Stringent manufacturing requirements.  |

#### 3.2. The Critical Role of Interconnect Standards

For chiplets from different vendors to be "plug-and-play," standardized communication interfaces are essential. The recent introduction of the Universal Chiplet Interconnect Express (UCIe) standard is a landmark development for the industry [7].

TABLE II. COMPARISON OF MAJOR DIE-TO-DIE (D2D) INTERCONNECT STANDARDS.

| Feature              | UCIe                                                                                         | BoW<br>(Bunch of<br>Wires)                                         | AIB (Advanced Interface Bus)                                       |

|----------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| Description          | Comprehensive<br>open standard<br>for physical<br>layer, protocol,<br>and software<br>stack. | Simple,<br>open<br>physical<br>layer<br>specification<br>from OCP. | Open-sourced parallel interface from Intel; a foundation for UCIe. |

| Protocol<br>Support  | Leverages PCIe® and CXL <sup>TM</sup> ecosystems.                                            | Protocolagnostic.                                                  | Protocolagnostic.                                                  |

| Packaging<br>Support | Standard (2D) and Advanced (2.5D/3D).                                                        | Primarily standard (2D).                                           | Advanced (2.5D).                                                   |

| Industry<br>Traction | High (Intel, AMD, TSMC, Samsung, etc.)                                                       | Moderate, for specific use-cases.                                  | Historical, foundational.                                          |

| Primary<br>Use-Case  | Dominant<br>standard for<br>future plug-<br>and-play<br>chiplets.                            | Flexible,<br>low-<br>overhead<br>baseline for<br>research.         | Served as a key precursor technology.                              |

UCIe: This consortium-driven standard aims to create a universal chiplet ecosystem. It defines everything from the electrical and physical link to the protocol stack, supporting high bandwidth and low latency across both standard and advanced packages [7].

BoW (Bunch of Wires): An open specification from the Open Compute Project (OCP) that provides a simple and efficient

physical layer for D2D links, offering design flexibility [9].

• AIB (Advanced Interface Bus): Developed by Intel and open-sourced, AIB was a foundational technology that heavily influenced the development of UCIe's advanced packaging profile [7].

#### **Thermal Management and Reliability Challenges**

The integration density in chiplet systems, especially in 3D stacks, creates intense "hotspots" that are difficult to manage, as heat from upper layers must pass through lower layers to dissipate [10].

➤ Heat Dissipation Challenges: The vertical stacking in 3D ICs creates a longer thermal path to the heat sink, potentially degrading the performance and reliability of all chiplets in the stack.

#### ➤ Mitigation Strategies:

- Advanced Thermal Interface Materials (TIMs): Developing TIMs with superior thermal conductivity is critical for efficient heat transfer from the chip to the heat sink [10].

- Microfluidic Cooling: An emerging and potent solution that involves etching microscopic channels for coolant directly into the silicon or package, offering extreme cooling capabilities [8].

- Simulation and Modeling: Advanced thermo-mechanical simulation tools are essential for predicting thermal profiles and mechanical stresses caused by Coefficient of Thermal Expansion (CTE) mismatch between different materials.

### The Role of AI/ML in Chiplet System Co-Design

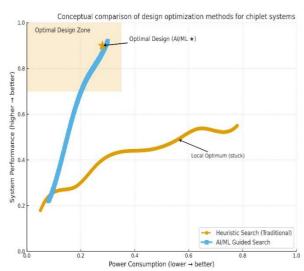

The design space for chiplet systems is vast and complex, making traditional optimization methods slow and inadequate. Artificial Intelligence and Machine Learning (AI/ML) are now indispensable tools for navigating this complexity.

- Intelligent Placement and Routing: ML models can rapidly explore millions of possible chiplet arrangements and interconnect configurations to optimize for performance, power consumption, and signal integrity, reducing design time from weeks to days [11].

- Proactive Resource Management: As highlighted in [12], ML can be used at runtime to predict traffic congestion and dynamically configure network-on-package (NoP) resources like link bandwidth and voltage/frequency levels, improving energy efficiency.

- Reliability and Yield Prediction: AI can analyze manufacturing and test data to predict failure rates and identify potential reliability risks before mass production.

Fig. 2 Conceptual comparison of design optimization methods for chiplet systems.

### **Emerging Integration Directions**

The chiplet concept is expanding beyond digital logic, embracing the "More-than-Moore" trend by integrating diverse technologies.

- Co-Packaged Optics (CPO): Integrating silicon photonics chiplets for optical data transfer alongside electronic processing chiplets. This overcomes the bandwidth and power limitations of electrical I/O wires, a critical need for future data centers [8].

- Heterogeneous Sensor Fusion: Combining chiplets for sensing (e.g., image, LiDAR), processing, and memory into a single package. This enables ultra-compact, high-performance systems for autonomous vehicles, robotics, and IoT devices [2].

# Manufacturing, Testing, and Security

The economic viability of chiplet systems hinges on robust manufacturing, testing, and security practices.

- Known-Good-Die (KGD) and Testing: The chiplet model relies on the availability of KGD. This requires rigorous testing of each unpackaged chiplet. Built-in self-test (BIST) structures are essential for diagnosing failures after assembly into a complex system.

- Hardware Security: A system composed of chiplets from a global supply chain has a larger "attack surface." Threats include intellectual property (IP) theft, hardware Trojans, and side-channel attacks on the communication links between chiplets. Standards like UCIe are incorporating security features, but this remains a critical area of ongoing research [7, 13].

#### **Future Outlook and Research Opportunities**

The chiplet revolution is still in its early stages. Key future trends and open research problems include:

Chiplet Marketplaces and Open Ecosystems: The emergence of a vibrant ecosystem where designers can source standardized chiplets from

- a global marketplace, similar to the PCB component industry today. UCIe is the foundational step towards this vision [7].

- Integration with Disruptive Technologies: Exploring how chiplet interfaces can be adapted for emerging paradigms like quantum computing control systems or neuromorphic computing cores.

- Sustainability: The chiplet model can promote a circular economy by enabling the repair and upgrade of systems by replacing individual chiplets. Research into eco-friendly packaging materials and energy-efficient manufacturing processes is crucial [1].

- Open Challenges: Key research problems for the next decade include: achieving sub-micron 3D integration pitches, developing holistic codesign tools that simultaneously optimize for thermal, power, and performance, and establishing universal testing and security standards for a global supply chain.

#### 2. CONCLUSION

The transition to chiplet-based architectures represents a fundamental and necessary evolution for the semiconductor industry. By leveraging advanced packaging, standardized interconnects like UCIe, and AI-driven design tools, chiplet systems overcome the limitations of monolithic scaling. While significant challenges in thermal management, security, and testing remain, the path forward is clear. The collaborative development of an open chiplet ecosystem promises to accelerate innovation, delivering more powerful, efficient, and specialized computing systems for the future..

#### .. REFERENCES

- 1. R. H. Dennard et al., "Design of ion-implanted MOSFET's with very small physical dimensions," IEEE J. Solid-State Circuits, vol. JSSC-9, no. 5, pp. 256–268, Oct. 1974.

- 2. J. H. Lau, "Recent Advances and Trends in Heterogeneous Integration," ASME Journal of Electronic Packaging, vol. 145, no. 1, Mar. 2023.

- 3. S. Naffziger et al., "Pioneering chiplet technology and design for the AMD EPYC and Ryzen processor families," in Proc. ISCA, 2021, pp. 57–70.

- 4. Intel Corporation, "Intel Foveros Direct: Enabling Sub-10μm Pitch 3D Integration," in Proc. ECTC, 2024, pp. 1124–1129.

- 5. TSMC, "System on Integrated Chips (SoIC) and CoWoS Advanced Packaging," Technology Symposium, Hsinchu, Taiwan, 2023.

- 6. G. H. Loh and R. Swaminathan, "The next era for chiplet innovation," in Proc. DATE, 2023, pp. 1–6.

- 7. UCIe Consortium, "UCIe Specification Version 1.1," 2024.

- 8. M. S. Bakir and A. Naeemi, "Interconnect and Packaging Technologies for Heterogeneous Integration," Nature Electronics, vol. 3, no. 5, pp.

- 262–273, May 2020.

- 9. Open Compute Project (OCP), "Bunch of Wires (BoW) Specification Revision 1.0," 2023.

- 10. K. Mohan and L. Pate, "Advanced Thermal Management Solutions for 3D Stacked Die Packages," IEEE Trans. Compon., Packag., Manuf. Technol., vol. 13, no. 4, pp. 501–512, Apr. 2023.

- 11. S. Das et al., "Optimizing 3D NoC design for energy efficiency: A machine learning approach," in Proc. ICCAD, 2015, pp. 705–712.

- 12. M. F. Reza, "Machine Learning Enabled Solutions for Design and Optimization Challenges in Networks-on-Chip," ACM J. Emerg. Technol. Comput. Syst., vol. 19, no. 3, Article 23, 2023.

- 13. R. Manju, A. Das, J. Jose, and P. Mishra, "SECTAR: Secure NoC using Trojan aware routing," in Proc. NOCS, 2020, pp. 1–8.

- 14. J. Kim and N. S. Kim, "Special issue on emerging system interconnects," IEEE Micro, vol. 43, no. 2, pp. 6–8, Mar. 2023.

- 15. A. Das, E. Russo, and M. Palesi, "Multi-objective hardware-mapping co-optimisation for multi-DNN workloads on chiplet-based accelerators," IEEE Trans. Comput., vol. 73, no. 8, pp. 1883–1898, Aug. 2024.

- 16. M. Wade et al., "TeraPHY: A chiplet technology for low-power, high-bandwidth in-package optical I/O," IEEE Micro, vol. 40, no. 2, pp. 63–71, Mar. 2020.

- 17. P. P. Pande, "The future of on-chip and chipscale interconnects for next-generation computing systems," in Proc. IEEE Int. Conf. Comput. Design (ICCD), 2023, pp. 1-8.

- 18. R. G. Kim, J. R. Doppa, P. P. Pande, D. Marculescu, and R. Marculescu, "Machine learning and manycore systems design: A serendipitous symbiosis," Computer, vol. 51, no. 7, pp. 66–77, July 2018.

- 19. S. Naffziger et al., "'Zeppelin': An SoC for multichip architectures," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 40–42.

- 20. Y. Zhang and L. P. Huang, "A Survey of Security Challenges and Countermeasures in Chiplet-Based Systems," ACM J. Emerg. Technol. Comput. Syst., vol. 20, no. 1, Article 5, Jan. 2024.

- 21. K. Wang, A. Louri, A. Karanth, and R. Bunescu, "IntelliNoC: A holistic design framework for energy-efficient and reliable on-chip communication for manycores," in Proc. Int. Symp. Comput. Architecture (ISCA), 2019, pp. 589–600.

- 22. J. H. Lau, "Heterogeneous Integrations," in Semiconductor Advanced Packaging, Springer, New York, NY, 2021, pp. 1-34.

- 23. M. F. Reza, "Deep reinforcement learning enabled self-configurable networks-on-chip for high-performance and energy-efficient computing systems," IEEE Access, vol. 10, pp. 65339–65354, 2022.

- 24. A. Sebastian, M. Le Gallo, R. Khaddam-Aljameh, and E. Eleftheriou, "Memory devices and applications for in-memory computing," Nature Nanotechnol., vol. 15, no. 7, pp. 529–544, Jul. 2020.

- 25. S. Abadal, C. Han, and J. M. Jornet, "Wave propagation and channel modeling in chip-scale wireless communications: A survey from millimeter-wave to terahertz and optics," IEEE Access, vol. 8, pp. 278–293, 2020

- 26. Y. Shim and D. Oh, "Design and technology spaces for heterogeneous chiplet integration," Design

the Solution, 2022. [Online]. Available: https://designthesolution.org/wp-content/uploads/2022/09/Design-and-technology-spaces-for-heterogeneous-chiplet-integration.pdf

Advances in Consumer Research